Aries bases SoM on Microchip’s PolarFire SoC FPGA

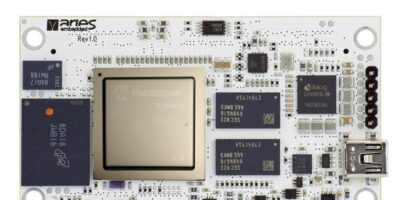

Based on Microchip’s PolarFire SoC FPGA, the M100PFS system on module (SoM) from Aries takes advantage of the FPGA’s 64bit RISC-V multi-core processor subsystem with low-power FPGA technology.

Andreas Widder, MD of Aries Embedded, explained that it allows customers to use the low power PolarFire SoC’s hardened real-time, Linux-capable, RISC-V processor subsystem to benefit applications that require low power consumption, thermal efficiency, and defence-grade security for a variety of embedded systems that require deterministic operation.

The M100PFS FPGA SoM is suited for secure, power-efficient computation in smart embedded vision, industrial automation, communications and industrial IoT.

The small SoM measures 74 x 42mm and runs with low device static power, low inrush current and low-power transceivers. The PolarFire FPGA technology offers single-event upset (SEU) immunity, built-in single error correction, double error detection (SECDED) and large SRAM interleaving built into the FPGA fabric. SECDED runs on all processor memory resources and the system controller suspend mode serves safety-critical designs, says Aries.

For security, there is also Cryptography Research Incorporated (CRI)-patented differential power analysis (DPA) bit stream protection, integrated dual physically unclonable function (PUF), and 56kbyte of secure, non-volatile memory (sNVM).

The PolarFire SoC combines a quad 64bit RISC-V 64GC core and a 64bit RISC-V 64 IMAC monitor core. The SoM uses the FCVG484 package that scales from the PolarFire SoC’s 23k logic element (LE) device up to the 250k LE device.

A SoM offering the largest 460k LE PolarFire SoC device will be offered in later versions, advises the company. The RISC-V CPU micro-architecture implementation is a simple five-stage, single issue, in-order pipeline that is immune to the Meltdown and Spectre exploits found in common out-of-order machines.

All five CPU cores are coherent, with the memory subsystem allowing a mix of deterministic real-time systems and Linux in a single multi-core CPU cluster. Processor I/Os include two Gigabit Ethernet, USB 2.0 OTG, two CAN 2.0 A and B, Execute in place quad SPI flash controller, five multi-mode UARTs, two SPI, two I2C, RTC, GPIO, and five watchdog timers. Memory comprises 1/2/4Gbyte LPDDR4 RAM dedicated to the HMS, 1/2/4Gbyte LPDDR4 RAM dedicated to the FPGA, 32 Mbit NOR Flash, and four to 64Gbyte eMMC memory. The default configuration contains Gigabit Ethernet, UART, CAN, SPI, I²C, and USB.

A prototype of the M100PFS SoM will be shown at Embedded World (25 to 27 February) Hall 3A, stand 441. Aries will start shipping boards to customers in Q4 2020.