3DIC Compiler accelerates multi-die system design and integration

Capabilities for advanced multi-die system design in a single environment are offered by the 3DIC Compiler, part of the Synopsys Fusion Design platform. It offers powerful 3D viewing capabilities which provide an intuitive environment for 2.5D/3D package visualisation and significantly reduces design to analysis iterations and minimises the overall integration time

According to Synopsys, it provides integration with Ansys’ silicon package PCB technology for system-level signal, power and thermal analysis, explains Synopsys.

According to Synopsys, it provides “an unprecedented fully integrated, high-performance, and easy-to-use environment” for architectural exploration, design, implementation, and sign off with signal, power, and thermal integrity optimisation in a single compiler. IC design and packaging teams can achieve “unparalleled” levels of multi-die integration, co-design and faster time to convergence, claims the company.

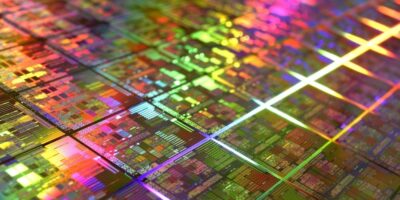

2.5 and 3D multi-die integration have become critical to meet system-level performance, power, area and cost requirements. Design teams are required to leverage multi-die integration to address new applications such as artificial intelligence (AI) and high-performance computing. These applications are driving new packaging architectures like chiplets and stacked-die, in combination with high-bandwidth or low-latency memory to be integrated in a package solution.

Traditional IC packaging tools have been integrated, often loosely, with existing IC design tools but they are fundamentally limited in scalability by their data models and begin to break with the more complex design requirements of recent complex 3DIC architectures. In addition, the disjointed tools and loosely integrated flows, mean that 3DIC design schedules are unpredictable, long, and frequently non-convergent, said Synopsys.

Synopsys’ 3DIC Compiler is built on an IC design data model – enabling scalability in capacity and performance with more modern 3DIC structures. It provides a single environment with planning, architectural exploration, design, implementation, analysis, and sign off and has visualisation capabilities such as 360 degree 3D view, cross probing for all views (architecture, planning, design, implementation, analysis, and sign off).

Synopsys has partnered with Ansys to integrate Ansys’ RedHawk family of silicon-proven analysis capabilities with 3DIC Compiler. RedHawk generates highly accurate signal, thermal and power data which are tightly integrated into 3DIC Compiler for package design. The automatic back-annotation between RedHawk and Synopsys’ 3DIC Compiler enables much faster convergence with fewer iterations than disjoint solutions.