Zuken enhances system level PCB design with intelligent layout and routing

The latest edition of CR-8000 advances system-level PCB design with significant enhancements in analogue simulation, signal integrity (SI) analysis, and intelligent layout and routing, says Zuken.

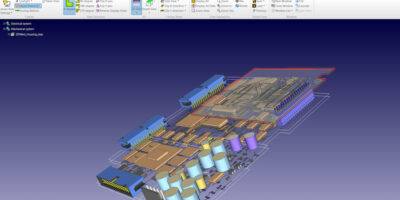

CR-8000 is a 3D electronic system design platform featuring seamlessly integrated applications for architectural planning, detailed engineering, physical layout, MCAD collaboration, and manufacturing optimisation. CR-8000 provides a unified environment for designing and verifying single and multi-board systems, including chip-scale packaging (CSP), multi-chip modules, and system-in-package technologies (SiP). CR-8000 is believed to be the only PCB design solution complemented by data management capabilities providing comprehensive library, module, configuration, and release management.

As electronic products become more complex, the need for early analysis has become more critical, says Zuken. CR-8000 2021 features over 150 enhancements across the tool suite ranging from architectural planning, system-level schematic design and verification, 3D multi-board and advanced packing layout, through to manufacturing outputs generation. The release puts specific emphasis on improved design efficiency via early analysis.

Particular attention was given to fine-tuning the constraint and simulation capabilities in System Planner and Design Gateway, CR-8000’s engineering front-end applications. The 2021 enhancements make marginal design problems more detectable with more robust constraint definition capabilities. For 3D multi-board layout and routing, Design Force has new place by area, template, and reuse functionality to apply existing placement and routing patterns on new designs.

As part of the early analysis focus, Design Gateway now supports the simulation of PCB parasitic effects in the circuit design stage through the ability to include parasitic element models in Spice simulations launched directly in the schematic. The simulation model library manager has a new user interface and is designed to handle today’s volume of model data smoothly. Importing models from various sources such as Ibis, Spice, or S-Parameters is presented uniformly at the user’s fingertips.

SI analysis functionality has been enhanced to support the execution of parameter sweeps across multiple pin models in one pass. A user can now explore the most suitable model parameters in a shortened timeframe. SI Analysis now considers a more accurate model for the surface roughness of the copper PCB material. The SI verification of differential pair routing now reports measurement results of crossing voltages in both tables and waveform display. User productivity has been improved by specifying automatic extraction and exporting of PI and EMI analysis results. Time-intensive analysis functions such as the Ibis AMI SerDes are now completed in less time, claims Zuken.

Design Force benefits from numerous new functions to help organise and streamline large designs. Users can now guide component placement for large boards based on schematic sheet component positioning. Exact placement and routing patterns from previous designs are reusable on new board designs with a ‘Create Used Board’ function. By creating specific functions for manual tasks such as creating anti-pads (protected areas around through-holes) or solder resist subtraction, design time is reduced.

The integration of Ansys simulation tools into Design Force has been extended to cover multi-physics analysis of multi-board designs to enable identification and correction of system-level design integrity issues. According to Zuken, this level of integration will reduce time-consuming and costly redesign efforts in advanced stages of the engineering process. Multi-discipline designs can be transferred to Ansys in a single EDB file for analysis of multi-board designs, including mechanical chassis and enclosure data.