High coverage tests can detect corner cases for SoC development

Building on Breker Verification Systems’ Cache Coherency Test, the company has released the System Coherency Synthesis TrekApp to generate thousands of high coverage tests to stress cross-system coherency and detect corner cases for SoC and processor design.

It uses abstract models of common and novel algorithms to automatically generate coherency test content for multi-agent system platforms based on coverage directives. The TrekApp can be configured for Arm, RISC-V and other processor configurations as well as a range of storage and I/O architectures, says Breker.

“System coherency is an increasingly complex and error-prone challenge for many SoC platforms that requires considerable expertise and effort to accomplish,” said Adnan Hamid, Breker’s executive president and CTO. “Our Test Suite Synthesis technology produces dramatic improvements in test composition time and coverage over manual tests and basic test generators including templating schemes,” he added.

The increase in SoC complexity and diverse processor architectures poses a coherency challenge which is addressed by the TrekApp, using Test Suite Synthesis technology to address coherency across the entire system, including fabric and I/O issues as well as advanced memory architectures more effectively than zero abstraction templating and similar schemes, claimed the company.

The TrekApp leverages established methods such as the Dekker algorithm, the Moesi state protocol for system-wide testing, stride testing, false sharing analysis and other exclusive test mechanisms.

Coupled with processor integration tests for Arm v8/v9 and the RISC-V instruction set architecture (ISA) the TrekApp generates comprehensive test content for most SoCs in development today. Specialised custom instructions or complete instruction sets can be included and alternative test algorithms can be inserted, crossing test content output results for high verification coverage.

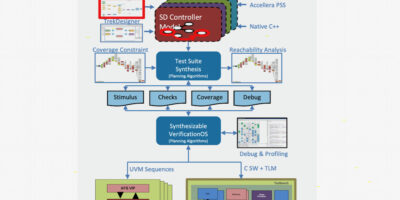

The System Coherency TrekApp generates C code and transactions for system-level testbenches or universal verification methodology (UVM) sequences for cache unit and sub-system simulation. It operates on virtual prototype platforms, simulation, emulation, FPGA prototyping or final silicon, and enables the full debug and profiling of the device under test on those platforms.

The System Coherency Synthesis TrekApp is part of the Breker TrekApp library that provides automated test content for cache coherency, Arm and RISC-V integration, power domain management, security and network traffic generation. TrekApps operate on the Breker Test Suite Synthesis Solution and Synthesizable VerificationOS for automated, coverage-driven test generation for a variety of multi-threaded platforms from a single, easy-to-understand specification model.

System Coherency Synthesis TrekApp is available now from Breker Verification Systems.