Tensilica Xtensa LX processor delivers enhanced power efficiency and performance

To deliver pervasive intelligence at the edge, Cadence has introduced the eighth generation of its extensible Tensilica processor platform, Xtensa LX.

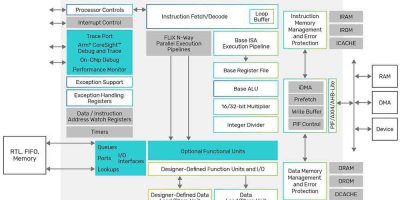

It offers “significant” new capabilities to address the increasing system level performance and AI requirements of processor-based SoC designs, said the company, while still providing energy-optimised Tensilica IP.

Enhancements are driven by the push for pervasive intelligence at the edge in the automotive, consumer and deeply embedded computing markets, said Cadence. The Xtensa LX8 platform will be the foundation for processor and system level designs, including new DSP, multi-processor, interconnect and system-level IP products.

When scaling processor performance to meet increasing performance demands of intelligent edge devices, it is not enough to simply scale clock frequency or add additional processors, and factors such as data movement, memory bandwidth, latency, advised Cadence. In addition, ease of integration is critical as SoC designs grow more complex. For example, recurrent and convolutional neural networks often include large datasets that must be quickly accessed from system memory in order to meet real-time requirements. Processor and DSP subsystems must now support multiple concurrent algorithms and ever-larger width filters, so the ability to reduce the latency of memory accesses and limit DMA transfers of repetitive zeroes can greatly improve overall system performance. The Xtensa platform enhancements will be leveraged across the family of Tensilica HiFi Vision, ConnX and FloatingPoint DSPs and AI controllers. For example, the L2 cache performance has been improved by 50 per cent or more for cache-based subsystems compared to the Xtensa LX7 processor and reduces pressure on L1 caches, said Cadence. Another enhancement is improved branch prediction which is claimed to be “significant” acceleration in control-code performance

Enhanced Arm AMBA interfaces in both original AMBA 4 AXI interconnect, for easy integration into high performance devices, and low latency APB interface, further improve system performance while reducing pressure on the primary system bus, added the company.

Enhanced iDMA improves 3D DMA transfers found in complex DSP algorithms while also adding compression/decompression support and expanding the physically addressable memory to 40 bits. There is also expanded interrupt support to ensure up to 128 interrupts can be accommodated to service the most demanding system level requirements, said Cadence.

The Tensilica Xtensa LX8 processor is currently shipping to early access customers, with general availability expected in late Q3 2023.