Aldec accelerates simulation targeting Microchip FPGAs

The latest release of hardware assisted register transfer level (RTL) simulation acceleration for Microchip FPGA designs has been announced by Aldec. The HES-DVM simulation acceleration flow is for Microchip’s PolarFire, SmartFusion2 and RTSX/RTAX FPGA designs using Aldec’s HES-MPF500-M2S150 prototyping board.

Simulation acceleration techniques have been around for about two decades, but most products are based on FPGAs from one or two leading FPGA vendors. Usually, it does not matter which FPGA family is used on the simulation acceleration board if the design is coded using synthesizable RTL.

Growing design complexity, along with shrinking design cycles and shorter time to market, steer engineers down the path of re-usable IP blocks from the FPGA vendor, instead of developing RTL code. This has a drawback in that the designs become dependent on the given FPGA technology, and the re-usable IP blocks usually require far more computational power to simulate than pure RTL code.

Aldec says the HES-DVM overcomes these challenges and removes a key verification bottleneck. The latest release of the HES-DVM EDA tool lets users of PolarFire, RTAX/RTSX and SmartFusion2 devices take advantage of Microchip IPs to accelerate their RTL simulations using Aldec’s HES-MPF500-M2S150, which features the largest devices available in both families.

“Aldec has a long history of developing hardware assisted verification solutions, with our first HES board and simulation acceleration platform released 20 years ago,” said Zibi Zalewski, general manager of Aldec’s hardware division. “We also have a proven track record of developing Microsemi/Microchip FPGA prototyping boards, and it is great that we can combine these areas of expertise to meet today’s verification challenges.”

The 2020.09 software release of HES-DVM is available immediately.

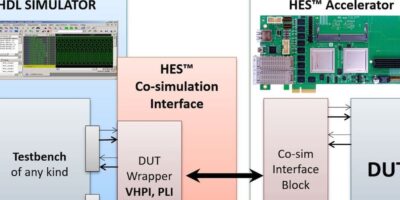

HES-DVM is a fully automated and scalable hybrid verification environment for SoC and ASIC designs. Utilising the latest co-emulation standards like SCE-MI or TLM and the newest FPGA technology, hardware and software design teams obtain early access to the hardware prototype of the design. HES-DVM is used in labs worldwide for all kinds of emulation and physical prototyping tasks including simulation acceleration, hybrid virtual prototypes, in-circuit emulation, software validation and prototyping.

Aldec offers a portfolio of HES prototyping boards based on the largest Xilinx FPGAs of the Virtex UltraScale Plus, UltraScale and Virtex-7 families, Microsemi PolarFire and SmartFusion2. The boards are architected to allow for easy expansion using BPX backplane and standardised FMC and BPX daughter card connectors.

Established in 1984, Aldec is an industry leader in electronic design verification and offers a patented technology suite including RTL design, RTL simulators, hardware-assisted verification, SoC and ASIC prototyping, design rule checking, CDC verification, IP cores, high performance computing platforms, embedded development systems, requirements lifecycle management, DO-254 functional verification and military/aerospace solutions.