Ceva claims Gen4 XC is most powerful DSP architecture

Offering a performance of 1,600 Giga operations per second (GOPS), the Gen4 Ceva-XC architecture has been revealed by the company. It also has dynamic multi-threading and advanced pipeline to reach operating speeds of 1.8GHz at 7nm.

It targets 5G intelligent radio access networks (RAN) and enterprise access points and other multi-Gbit, low latency applications, with 2.5X improvement in peak performance, claims Ceva.

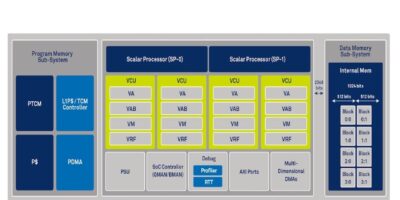

The Gen4 Ceva-XC’s scalar and vector processing enables two-times eight-way VLIW and up to 14,000 bits of data level parallelism. It incorporates an advanced, deep pipeline architecture enabling operating speeds of 1.8GHz at a 7nm process node. The physical design architecture can be used for a fully synthesisable design flow and a multi-threading design. Processors can be dynamically reconfigured as either a wide SIMD machine or divided into smaller simultaneous SIMD threads.

The Gen4 Ceva-XC architecture’s memory subsystem, uses 2048-bit memory bandwidth and has coherent, tightly-coupled memory to support efficient simultaneous multi-threading and memory access, says Ceva.

The first processor based on the Gen4 CEVA-XC architecture is the multi-core Ceva-XC16, the fastest DSP ever made, says the company. It is intended for the rapid deployment of different form factors of 5G RAN architectures including Open RAN (O-RAN), baseband unit (BBU) aggregation as well as Wi-Fi and 5G enterprise access points. The CEVA-XC16 is also suitable for massive signal processing and AI workloads associated with basestation operation.

The Ceva-XC16 has been specifically architected with the latest 3GPP release specifications in mind, and is already in design with a leading wireless vendor for its next-generation 5G ASIC.

The high parallelism can be reconfigured as two separate parallel threads. These can run simultaneously, sharing L1 data memory with cache coherency to improve latency and performance efficiency for PHY control processing, without the need for an additional CPU, advises Ceva. This boosts performance per square mm by 50 per cent compared to a single-core/single-thread architecture when large numbers of users are connected in a crowded area. This saves 35 per cent die area for a large cluster of cores, for example custom 5G basestation silicon, Ceva notes.