Codasip expands support package for RISC-V SweRV cores

Configurable RISC-V embedded processor IP provider, Codasip has extended its SweRV support package to include Western Digital’s SweRV EH2 and SweRV EL2 RISC-V cores. The cores are available to the open-source community through CHIPS Alliance, an open-source development organisation which seeks to provide a barrier-free environment to allow collaboration for open-source software and hardware code.

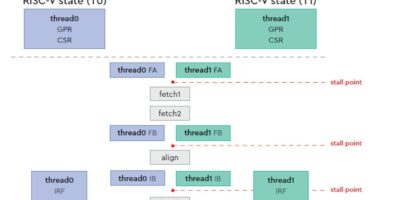

The SweRV Core EH2 is a high-performance 32-bit, dual-thread, superscalar, nine-stage pipeline core with simulated performance of up to 6.3 CoreMark/MHz and a footprint of 0.067mm2 on TSMC’s 16nm CMOS process technology. The core supports the RISC-V RV32IMAC instruction set and bit manipulation extensions.

The SweRV Core EL2 is a second-generation SweRV core aimed at medium-performance embedded applications. It is a 32-bit, single issue with a four-stage pipeline with simulated performance of 3.6 CoreMark/MHz and supporting the RISC-V RV32IMC instruction set.

The dual thread SweRV EH2 delivers outstanding embedded performance and the EL2 great silicon efficiency. Our SweRV Support Package will enable their rapid adoption in the market, said Přemysl Václavík, senior director Open IP, Codasip. The company believes this will help to accelerate the RISC-V ecosystem.

The SweRV Support Package, developed by Codasip in co-operation with Western Digital, provides a comprehensive set of tools and components needed to design, implement, test, and write software for a SweRV core-based system-on-chip, integrated into a single environment. The Free version aimed at the educational market contains support for the software toolchain, open-source EDA tools, design flow integration, and a user forum. The Pro version additionally provides support for commercial EDA flows and professional customer support.

Codasip supplies processing solutions for IC designers. It offers solutions based on open standards such as the RISC-V ISA, LLVM and UVM. It is a founding member of the RISC-V Foundation and was the first company to offer a commercial RISC-V IP core in 2015.

RISC-V is an open, free ISA. It enables designers to take advantage of a standard base instruction set for software portability, with a choice of standard or custom extensions to enhance computational performance.