EDA design kit enhances SiP design and verification

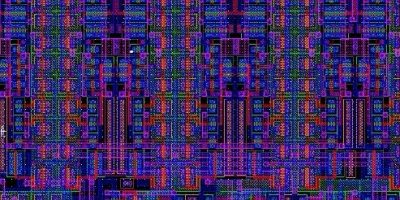

Advanced Semiconductor Engineering (ASE) and Cadence Design Systems have collaborated to release a system in package (SiP) EDA toolset that addresses the challenges of designing and verifying fan-out chip-on-substrate (FOCos) multi-die packages.

There is the SiP-id (System-in-Package – intelligent design) design kit, an enhanced reference flow including IC packaging and verification tools from Cadence, and a new methodology that aggregates the requirements of wafer-, package- and system-level design into a unified and automated flow. By deploying the SiP-id methodology, designers can reduce design iterations and improve throughput as compared to existing advanced packaging EDA tools, reducing the time needed to design and verify complex SiPs.

Before this design kit, IC packaging engineers leveraged standard EDA design tools coupled with a set of loosely defined rules to lay out their packages. However, this approach has many limitations when designing today’s advanced multi-die packages. To provide a more holistic approach to the design and verification of SiP and advanced fan- out packages, ASE and Cadence collaborated to develop a design kit, methodology, and streamlined and automated reference flow using enhanced Cadence IC packaging and verification tools, tailored for ASE’s advanced IC package technologies. In a typical use-case with high-pin-count dies, packaging engineers using SiP-id and the accompanying reference flow and methodology were able to reduce time from more than six hours to 17 minutes, compared to existing tools with manual operation, records Cadence.

SiP-id is immediately available from ASE.

Cadence enables electronic systems and semiconductor companies to create the innovative end products that are transforming the way people live, work and play. Cadence software, hardware and semiconductor IP are used by customers to deliver products to market faster. The company’s System Design Enablement strategy helps customers develop differentiated products—from chips to boards to systems—in mobile, consumer, cloud data centre, automotive, aerospace, IoT, industrial and other market segments.

The ASE Group provides independent semiconductor manufacturing services in assembly, test, materials and design manufacturing. It develops and offers a portfolio of technology and solutions including IC test program design, front-end engineering test, wafer probe, wafer bump, substrate design and supply, wafer level package, flip chip, system-in-package (SiP), final test and electronic manufacturing services through USI Inc and its subsidiaries, members of the ASE Group.