Imec demonstrates two-metal layer back-end-of-line for the 3nm node

At this week’s technology forum ITF USA 2019, imec presents a dual-damascene 21nm pitch test vehicle relevant for manufacturing the 3nm logic technology node. With this test vehicle, a 30 per cent improvement in resistance-capacitance (RC) product was obtained in comparison to previous generations, without impacting reliability, reports the research hub. The need for implementing scaling boosters such as self-aligned vias and self-aligned blocks in 3nm and beyond interconnect technologies has been demonstrated.

While the dimensional scaling of traditional front-end technologies is expected to slow down, the back-end-of-line dimensions keep on scaling with around 0.7 times to keep up with the required area scaling. For the 3nm logic technology node, M2 interconnect layers with metal pitches as narrow as 21nm need to be manufactured while preserving the back-end-of-line’s performance, explains imec. This implies a tight control of the RC delay, while maintaining good reliability.

The forum was the opportunity for imec to demonstrate for the first time, a dual-damascene 21nm metal pitch test vehicle that is relevant for the 3nm technology node. In addition to the improved RC, the test vehicle also performs well in terms of reliability, with no electromigration failures observed after 530 hours at 330 degrees C, and dielectric breakdown (TDDB) measurements demonstrated a time-to-failure

Above 10 years at 100 degrees C.

To pattern the M2 layer, a hybrid lithography approach was proposed, using 193nm immersion-based self-aligned quadrupole patterning (SAQP) for printing the lines and trenches, and extreme ultra violet lithography

The test vehicle implemented a barrier-less ruthenium (Ru) metallisation scheme and an insulator with dielectric constant k = 3.0.

First results also demonstrate that the proposed interconnect technology can be improved by adding scaling boosters, including buried power rail, SuperVia, self-aligned blocks, fully self-aligned vias and double self-aligned blocks.

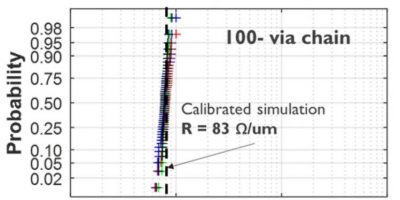

The image shows the measured resistance per link for 100 via chains with 21nm metal pitch shows excellent agreement with simulation (left) and elemental mapping of Ru lines and vias (right)