Mentor streamlines IC verification with automated analysis

To help IC designers accelerate design closure, Mentor, a Siemens business, has extended its Calibre Recon technology to the Calibre nmLVS circuit verification platform. Calibre Recon is an extension to Mentor’s Calibre nmDRC suite and is designed to enable customers to rapidly, automatically and accurately analyse IC designs for errors during early-stage verification design iterations. According to Mentor, this significantly shortens design cycles and results in a faster time to market.

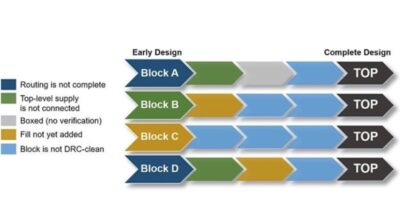

The Calibre nmLVS-Recon helps speed overall circuit verification turnaround time by helping SoC engineers, circuit designers, and IC circuit verification teams identify and resolve selected systemic errors early in the development phase. Such violations can consume resources and potentially generate millions of error results, many of which are due solely to the incomplete status of the design. Use of the Calibre nmLVS-Recon results in a 10-fold improvement in runtime and three times less memory requirements when analysing early stage designs, says Mentor.

“By combining the Calibre nmLVS-Recon technology with Samsung’s existing certified sign-off Calibre nmLVS design kits, our mutual customers will experience faster iterations on early ‘dirty’ designs, driving accelerated LVS verification cycles. All of this will help mutual customers tape out sooner at Samsung,” said Jongwook Kye, vice president of the Design Enablement Team at Samsung Electronics.

Calibre nmLVS-Recon technology is based on a flexible configuration framework that enables multiple use models, allowing design teams to select and analyse specific classes of circuit verification issues. The tool features automated, intelligent execution heuristics engineered to help users seamlessly navigate between a complete Calibre nmLVS signoff flow and Calibre Recon selected circuit verification checks. Advanced options are for data partitioning, design breakdown, data reuse, task distribution, and error management, enabling the Calibre nmLVS-Recon flow to be used with any foundry/integrated device manufacturer’s (IDM) Calibre sign-off design kit “as is”, and on any process technology node.

Early versions of any design typically contain gross systemic violations, which generate errors and are compute intensive. Circuit verification engineers can use the Calibre nmLVS-Recon short isolation configuration to interactively and iteratively find and fix these types of violations quickly and efficiently.

“By adding the Calibre nmLVS-Recon technology to the Calibre platform, Mentor continues to address the specific challenges our customers face when designing increasingly sophisticated ICs,” said Michael Buehler-Garcia, vice president of Product Management for Calibre Design Solutions at Mentor. “The early design exploration that the Calibre nmDRC-Recon approach offers has already helped design teams shave hours, and in some customer experiences, even days off their circuit verification times. With Calibre nmLVS-Recon technology, Mentor now offers the same opportunity for total turnaround time reduction in circuit verification, while also helping design teams address the complexity they encounter in today’s chip designs.”

The Calibre nmLVS-Recon initial offering will be available to the market with the Calibre family release this month, with additional capabilities planned for later releases.