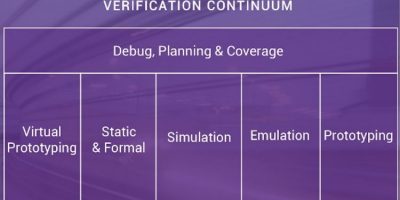

Native tools from Synopsys enhance verification continuum

Ahead of DAC, Synopsys announces a new release of its Verification Continuum with new native integrations across verification tools, enabling up to five times higher verification performance. Verification Continuum is built from what is claimed to be the industry’s fastest engines developed by Synopsys, including Virtualizer virtual prototyping, SpyGlass static and VC Formal verification technologies, VCS (Synopsys’ functional verification solution) simulation, ZeBu emulation, Synopsys HAPS prototyping, Verdi debug, and VC Verification IP (VIP).

New enhanced native integrations in Verification Continuum enable performance gains between all verification engines, accelerating time-to-market for complex SoC designs with increasing software content to meet time-to-market pressures, explains Synopsys.

The latest release delivers Smart Loading technology, enabled by Unified Compile with VCS, which accelerated the Verdi design load time. Additionally, enhanced native multi-threaded dumping cuts overhead by 50 per cent, and the new dynamic waveform aliasing technology enables three times smaller fast signal database (FSDB) size.

Native integration of SpyGlass and VCS Unified Compile enables seamless read of DesignWare IP and encrypted IP designs, to improve ease of use, says Synopsys, compared to previous black box IP support. Integration of Verdi’s Unified Debug interface with SpyGlass enables a consistent debug user experience across the verification flow, adds Synopsys.

The latest VC Formal release has enhanced engine optimisation and orchestration. Native integration of the VC Formal testbench analyser (FTA) application and Certitude functional qualification system enables 10 times faster quality assessment of testbench and assertions. This is achieved with a single compile and intelligent fault injection and scheduling for formal property verification.

Native integration across VCS and VC Verification IP delivers a two times acceleration in simulation performance through the use of optimisations between VCS and VC VIP leveraging native UVM technology and industry-leading constraint solver technology.

To accelerated VIP, emulation and simulation, there is a unified compile of design and testbench and low latency interface supporting a seamless mix of signal-level and transaction-level communication, combined with native integration of VCS, ZeBu, and Accelerated VIP. The combination delivers 10 to 100 times acceleration in simulation acceleration compared to simulation alone, reports Synopsys.

Availability is scheduled for June 2019.