Tektronix and Anritsu create PCIe 5.0 transceiver and reference clock

Two test giants have collaborated to develop a PCIe 5.0 transceiver and reference clock. Tektronix and Anritsu claim to be the first to offer early card electromechanical (CEM) fixtures for pre-compliance testing. They add that the collaboration enables “industry-leading receiver verification”.

PCIe 5.0 operates at 128Gbytes per second and the PCI-SIG (Special Interest Group) has already announced the PCIe 6.0 specification of 256Gbytes per second operation and with multi-level PAM4 signalling.

The server/storage industry is rapidly transitioning to PCIe 5.0 due to new requirements imposed by 400G Ethernet, cloud AI and modelling (co-processors), storage capacity, and NAND-based storage, explains Tektronix. This rapid progression brings new problems for test and measurement traditionally split into base silicon level validation and CEM compliance testing with the PCI-SIG.

The Tektronix-Anritsu collaboration includes a PCIe 5.0 base and CEM transceiver and reference clock.

“Electronics designers today demand future-proofing to protect their innovations’ longevity into tomorrow,” says Takeshi Shima, vice president of Anritsu. “Providing a solution through Gen6 gives our customers a sense of our commitment to stay with them on the cutting edge of development,” he continued.

David Bouse, PCI Express systems engineer at Tektronix, said that developers are faced with design challenges for PCIe 5.0, shorter time-to-market windows, as well as new standards specifications to understand and apply, and new compliance testing requirements. “It is vital to have a comprehensive test equipment and software solution in place prior to workshop certification,” he said. “Our PCIe 5.0 test and debug solution can easily guide the engineer through compliance testing and debug to ensure their design meets new standards with a high degree of confidence,” he added.

The PCIe 5.0 transceiver and reference clock was developed and continues to be aligned with the 5.0 Base specification, 5.0 CEM specification, and 5.0 test specifications.

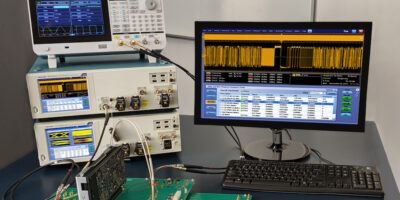

It includes a PCIe 5.0 automated base and CEM transmitter running on the DPO700000SX series real time oscilloscope and MP1900A Signal Quality Analyser-R series (BERT) from Anritsu. There is new receiver automation software from Tektronix with highly efficient algorithms for stressed eye calibration at 32GT per second and 16GT per second.

There is also support SigTest Phoenix with highly parallelised processing to reduce overall test time, mutiple form factors (M.2 and U.2) and varied clocking architectures (CC, SRNS and SRIS).

The test follows real time evolution of the 5.0 base specification with 32GT per second uncorrelated jitter and pulse width jitter measurements implemented to optimise A/D range and minimise noise, says Tektronix.

To address the challenges of 100MHz reference clock jitter and signal integrity measurements, there is an integrated PCIe Clock Jitter tool from Silicon Labs and Tektronix’s DPOJET tool.

According to Tektronix, the collaboration results in the industry’s first pre-compliance test fixtures for PCIe 5.0 CEM testing. It is available now, for use with DPO/MSO70000SX/DX.